Document No.

### AB-CO-Note 06-XX 1v4 (Tech.)

## CERN AB DEPARTMENT

CH-1211 Geneva 23 Switzerland CERN Div./Group or Supplier/Contractor Document No AB/CO/MI

EDMS Document No.

636589

Date: 16 OCTOBER 2006

## **TECHNICAL NOTE**

# USER INTERFACE TO THE BEAM INTERLOCK SYSTEM

#### Abstract

This note describes the functionality and the requirements of any User System's connection to the Beam Interlock System via the User Interface; this connection is critical for machine safety and must be implemented in a very specific manner to provide safe and reliable interlocking. The same unit is provided for all of the different applications of the Beam Interlock System; LHC ring, LHC injection, SPS ring and SPS Extraction & Transfer Lines.

| Written by :           |  |  |

|------------------------|--|--|

| B. Todd AB/CO          |  |  |

| A. Dinius AB/PO        |  |  |

| <b>B.</b> Puccio AB/CO |  |  |

## AB-CO-Note 06-XX 1v4 (Tech.)

Page 2 of 22

|          |            | Hi    | story of Cha | anges                  |

|----------|------------|-------|--------------|------------------------|

| Rev. No. | Date       | Pages |              | Description of Changes |

| 1.4      | 17-10-2006 | All   | Re-Release   |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

|          |            |       |              |                        |

## Page 3 of 22

### Table of Contents

| 1.                                                                                                                                                                             | OVERVIEW                                                                                                                                                                                                                                                                                                                     | 5                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                                            | INTRODUCTION                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                  |

| 1.2                                                                                                                                                                            | PURPOSE OF THIS DOCUMENT                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |

| 1.2.1                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

| 1.3                                                                                                                                                                            | AN IMPORTANT NOTE ABOUT REDUNDANCY                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                  |

| 1.4                                                                                                                                                                            | STRUCTURE OF THIS DOCUMENT                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                  |

| 2.                                                                                                                                                                             | THE ROLE OF THE USER INTERFACE                                                                                                                                                                                                                                                                                               | 7                                                                                                                                                                                  |

| 2.1                                                                                                                                                                            | INTERLOCKING THE LHC                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                  |

| 2.2                                                                                                                                                                            | INTERLOCKING THE SPS RING                                                                                                                                                                                                                                                                                                    | 9                                                                                                                                                                                  |

| 2.3                                                                                                                                                                            | INTERLOCKING THE SPS EXTRACTION AND TRANSFER LINES                                                                                                                                                                                                                                                                           | 10                                                                                                                                                                                 |

| 2.4                                                                                                                                                                            | INTERLOCKING THE LHC INJECTION                                                                                                                                                                                                                                                                                               | 11                                                                                                                                                                                 |

| 3.                                                                                                                                                                             | DESCRIPTION OF THE USER CONNECTION                                                                                                                                                                                                                                                                                           | 12                                                                                                                                                                                 |

| 3.1                                                                                                                                                                            | THE DIFFERENT TYPES OF USER SYSTEMS                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |

| 3.2                                                                                                                                                                            | HARDWARE INTERFACE SUPPLIED TO THE USER SYSTEMS                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                 |

| 3.2.1                                                                                                                                                                          | THE CIBUD                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 3.2.2                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

|                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

| 3.2.3                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

| 3.2.3<br><b>4.</b>                                                                                                                                                             | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | 15                                                                                                                                                                                 |

|                                                                                                                                                                                | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <b>15</b><br>15                                                                                                                                                                    |

| 4.                                                                                                                                                                             | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO                                                                                                                                                                                                                               | <b>15</b><br>15<br>16                                                                                                                                                              |

| <b>4.</b><br>4.1                                                                                                                                                               | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO<br>PINOLOGY OF USER CONNECTOR                                                                                                                                                                                                 | <b>15</b><br>15<br>16<br>17                                                                                                                                                        |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4                                                                                                                                          | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO<br>PINOLOGY OF USER CONNECTOR<br>USER SYTEM TO BIS INPUT/OUTPUT SPECIFICATIONS                                                                                                                                                | <b>15</b><br>16<br>17<br>18                                                                                                                                                        |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1                                                                                                                                 | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <b>15</b><br>15<br>16<br>17<br>18<br>18                                                                                                                                            |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2                                                                                                                        | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO<br>PINOLOGY OF USER CONNECTOR<br>USER SYTEM TO BIS INPUT/OUTPUT SPECIFICATIONS<br>GUARANTEED INPUT SPECIFICATIONS                                                                                                             | <b>15</b><br>16<br>17<br>18<br>18<br>18                                                                                                                                            |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b>                                                                                                           | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <b>15</b><br>16<br>17<br>18<br>18<br>18<br>18                                                                                                                                      |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b><br>5.1                                                                                                    | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO<br>PINOLOGY OF USER CONNECTOR<br>USER SYTEM TO BIS INPUT/OUTPUT SPECIFICATIONS<br>GUARANTEED INPUT SPECIFICATIONS                                                                                                             | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> </ol>                                                             |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b><br>5.1<br>5.2                                                                                             | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> </ol>                                                                         |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b><br>5.1<br>5.2<br>5.3                                                                                      | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> </ol>                                     |

| <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ol>                               | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS<br>GIVING USER_PERMIT<br>READING BEAM_INFO<br>PINOLOGY OF USER CONNECTOR<br>USER SYTEM TO BIS INPUT/OUTPUT SPECIFICATIONS<br>GUARANTEED INPUT SPECIFICATIONS<br>GUARANTEED OUTPUT SPECIFICATIONS<br>USER REQUIREMENTS<br>POWERING THE CIBU<br>USER SYSTEM TEST ON DEMAND | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> </ol> |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4<br>5.4.1                                                               | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>20</li> </ol>                                     |

| <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4.1</li> <li>4.4.2</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.4.1</li> <li>5.4.2</li> </ol> | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <b>15</b><br>15<br>16<br>17<br>18<br>18<br>18<br><b>19</b><br>19<br>19<br>19<br>20<br>20                                                                                           |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br><b>5.</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4<br>5.4.1                                                               | ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS                                                                                                                                                                                                                                                                          | <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>19</li> <li>19</li> <li>20</li> <li>20</li> <li>20</li> <li>20</li> </ol> |

## AB-CO-Note 06-XX 1v4 (Tech.)

Page 4 of 22

## List of Figures

| Figure 1: Simplified Internal Architecture of the LHC Beam Interlock System             | 8  |

|-----------------------------------------------------------------------------------------|----|

| Figure 2: Simplified Internal Architecture of the SPS Beam Interlock System             | 9  |

| Figure 3: Simplified Architecture of SPS Extraction and Transfer Lines Interlock System | 10 |

| Figure 4 : Simplified Internal Architecture of the LHC Injection Interlock system       | 11 |

| Figure 5: Rear View and Front View of the CIBU type D                                   | 13 |

| Figure 6: Rear View and Front View of the CIBU type S                                   | 13 |

| Figure 7: CIBUD Rear View                                                               | 14 |

| Figure 8: CIBU Tri-Colour Light-Emitting Diode Function                                 | 14 |

| Figure 9: Current Loop for USER_PERMIT                                                  | 15 |

| Figure 10: Optocoupler for BEAM_INFO                                                    | 16 |

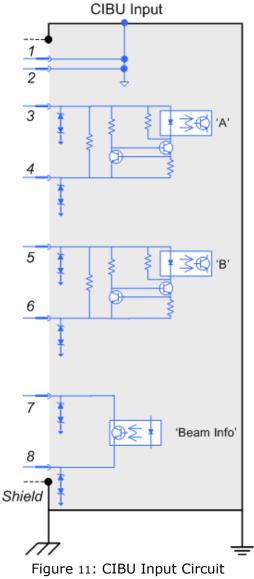

| Figure 11: CIBU Input Circuit Schematic                                                 | 17 |

| Figure 12: Principle of Interconnection for Complete EMC Compliance                     | 19 |

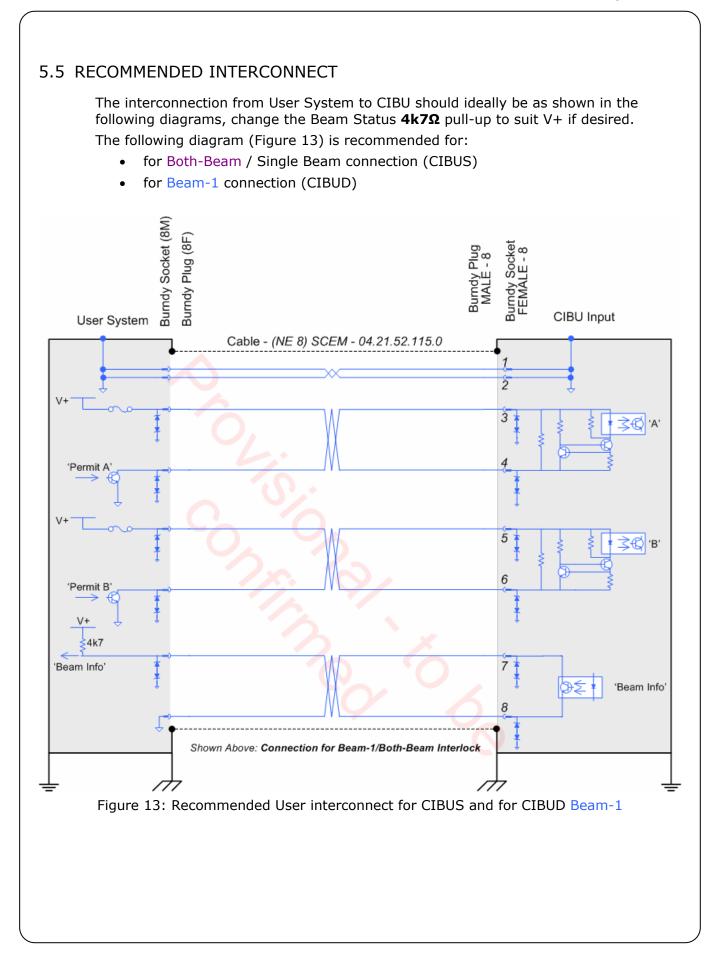

| Figure 13: Recommended User interconnect for CIBUS and for CIBUD Beam-1                 | 21 |

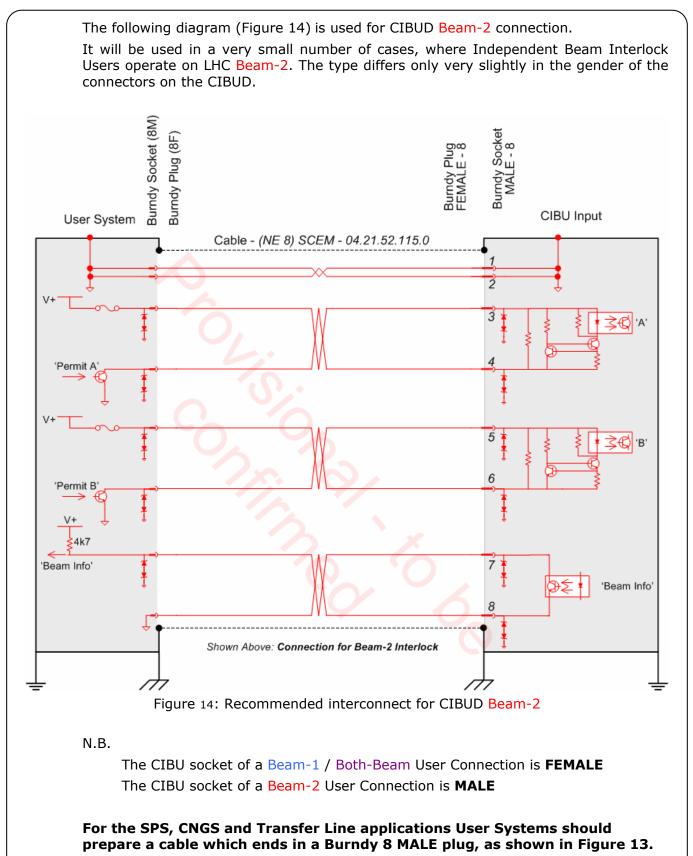

| Figure 14: Recommended interconnect for CIBUD Beam-2                                    | 22 |

## List of Tables

| Table 1: USER_PERMIT and BEAM_INFO Descriptions for LHC                   | 7  |

|---------------------------------------------------------------------------|----|

| Table 2: USER_PERMIT and BEAM_INFO Descriptions for SPS                   | 9  |

| Table 3 : USER_PERMIT and BEAM_INFO Descriptions for SPS Extraction Lines | 10 |

| Table 4: USER_PERMIT and BEAM_INFO Descriptions for LHC Injection         | 11 |

| Table 5: Basic Types of User System                                       | 12 |

| Table 6: Function of the Input Current Loops for USER_PERMIT              | 15 |

| Table 7 : Component List for USER_PERMIT                                  | 15 |

| Table 8: Function of the Output Transistor for BEAM_INFO                  | 16 |

| Table 9: Component List for BEAM_INFO                                     | 16 |

| Table 10: Pinology of CIBU User Connection                                | 17 |

| Table 11: CIBU Input Specifications                                       |    |

| Table 12: CIBU Output Specifications                                      | 18 |

LHC Project Document No. AB-CO-Note 06-XX 1v4 (Tech.)

Page 5 of 22

### **1. OVERVIEW**

#### 1.1 INTRODUCTION

The Beam Interlock System (**BIS**) was originally conceived and designed for the LHC, providing a fast, reliable and dependable mechanism for safe operation of the accelerator. During the design development it was always foreseen that the BIS would be capable of providing a robust modular solution for any other Beam Interlock System required by CERN. The BIS is expected to be deployed in four distinct, yet related environments:

- 1. The LHC ring

- 2. The SPS ring

- **3.** The SPS Extraction channels and Transfer Lines: (LSS4, TT40, TT41 & TI8) and (LSS6, TT60 & TI2).

- **4.** The LHC Injection

In all four cases, the same hardware is used to connect any **User System**<sup>i</sup> to the Beam Interlock System. Therefore, a unique User Interface (*CIBU*)<sup>ii</sup> is provided, fulfilling all the requirements of any of the three implementations.

The main priority in the development of the Beam Interlock System has been *safety*: it will respond when requested to with a very high level of safety, in fact, the BIS meets the IEC 61508 Safety Integrity Level 3 (*SIL 3*) that is to say the chances of the Beam Interlock System failing and not being able to respond to a User request are less than  $10^{-7}$ /h. The CIBU is intended to be installed in the User System's rack, giving a safe and reliable connection from User to BIS which is independent of User hardware, and of distance from User to BIS Rack.

#### 1.2 PURPOSE OF THIS DOCUMENT

The purpose of this document is to provide a detailed description of the interconnection from User System to BIS, in any of the three environments listed above. However it must also be understood that this document is only a *technical note*, complementing other engineering specifications ([1], [2], [3] and [4]) describing in detail the functionality and implementation of the BIS.

#### 1.2.1 REFERENCES

[1] The Beam Interlock System, Engineering Specification.

LHC-CIB-ES-0001-00-10 (EDMS Document No. 567256)

This document describes the functionality, architecture and performance requirements of the Beam Interlock System. In addition it defines the interfaces of the LHC BIS with the other systems

<sup>i</sup> Any equipment interconnected to the BIS with the purpose of interlocking is designated a User System

<sup>ii</sup> Following the LHC naming convention, this hardware is designated as **CIBU** (Controls-Interlocks-Beam-User) The CIBU is available in 2 versions: CIBU**S** (**single** type for one beam connection) and CIBU**D** (**double** type for beam1/beam2 connections)

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 6 of 22

[2] The Beam Interlock System Realisation, Engineering Specification (in preparation). Describing the LHC BIS implementation, explaining the design and realisation of the different hardware parts that compose the BIS, also covering the reliability, safety, availability and maintainability of the LHC BIS.

[3] The SPS Beam Interlock System, Engineering Specification (in preparation).

Describing the purpose and architecture of the SPS BIS, its functions, its interfaces with other systems, and its implementation based on the LHC BIS.

[4] Interlocking between SPS, CNGS, LHC transfer lines and LHC injection, Engineering Specification, LHC-CI-ES-0002 (EDMS Document No. 602470). Describing the SPS Extraction Lines BIS layout, discussing the implementation based on the LHC BIS. Also lists the expected Extraction Line Users.

### 1.3 AN IMPORTANT NOTE ABOUT REDUNDANCY

To meet the stringent SIL 3 requirements, and for CERN's accelerator complex to be suitably protected against beam related damage, the Beam Interlock System is completely redundant. This redundancy is performed using 2 separated channels (named **`A'** and **`B'**) from User System through to the Kicker systems. It is for this reason that two separate BEAM\_PERMIT inputs are required from the User System, labelled as **USER\_PERMIT `A'** and **USER\_PERMIT `B'**; ideally these two links should connect to two completely isolated pieces of hardware in the User System.

It has to be noted that *joining the redundant links together creates a singlemode failure in the interconnection, circumventing all BIS redundancy and thus having a huge impact on LHC safety. Explicit justification* is needed for any User System that will not provide a redundant USER\_PERMIT signal to the BIS.

### 1.4 STRUCTURE OF THIS DOCUMENT

The Beam Interlock System consists of identical modular hardware, however the end function carried out differs according to the scenario in which it is used. This document begins by briefly describing the functions and differences of each of the four main applications of the BIS.

The role of the User Interface for:

- *LHC Interlock* is described in section 2.1.

- SPS Interlock is described in section 2.2.

- SPS Extraction Interlock is described in section 2.3.

- *LHC Injection Interlock* is described in *section 2.4.*

Section 3 describes the CIBU function, showing diagrams with connector and LED locations.

Section 4 specifies the electronic interface required by the User System, with its requirements and implementation.

*Section 5* details other user requirements and the document concludes with complete diagrams of the preferred implementation of the interface.

## Page 7 of 22

## 2. THE ROLE OF THE USER INTERFACE

#### 2.1 INTERLOCKING THE LHC

The aim of the Beam Interlock System is to generate BEAM\_PERMIT signals for the two circulating LHC Beams.

When BEAM\_PERMIT is TRUE

» The related beam is allowed to circulate.

When BEAM\_PERMIT is FALSE

» A beam dump is requested (when BEAM\_PERMIT *changes* to FALSE).

More information is given in the dedicated engineering specification [1].

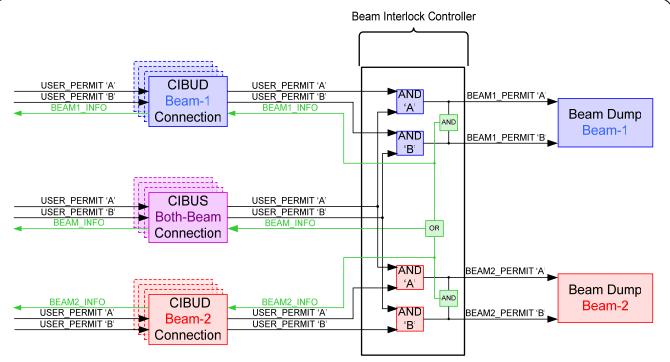

In LHC, the role of the CIBU is to take the two USER\_PERMIT signals and transmit them to the nearest Beam Interlock Controller in a safe and reliable manner. In return the Users receive a BEAM\_INFO giving an indication of the availability of the whole LHC machine for beam operation.

Two different families of User System are connected to the BIS:

1. Those interlocking Beam-1 and Beam-2 independently

» User connects twice, with Beam-1 and Beam-2 via a CIBUD (see 3.2.1).

- 2. Those interlocking Beam-1 and Beam-2 **simultaneously**

- » User connects once, with Both-Beam via a CIBUS (see 3.2.2).

| CIBU type &                 | US                                            | ER_PERMIT                                                                        | BEAM_INFO                                                                              |                                                                                                      |  |

|-----------------------------|-----------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| User<br>Connection          | TRUE                                          | FALSE                                                                            | TRUE                                                                                   | FALSE                                                                                                |  |

| <b>CIBUD</b><br>(Beam-1)    | Beam-1<br>allowed to<br>circulate             | Beam operation<br>NOT permitted <b>OR</b><br>dump request<br>for Beam-1          | All required Beam-1 User<br>Systems are available                                      | At least one required<br>Beam-1 User System is<br>unavailable                                        |  |

| <b>CIBUD</b><br>(Beam-2)    | Beam-2<br>allowed to<br>circulate             | Beam operation<br>NOT permitted <b>OR</b><br>dump request<br>for Beam-2          | All required Beam-2 User<br>Systems are available                                      | At least one required<br>Beam-2 User System is<br>unavailable                                        |  |

| <b>CIBUS</b><br>(Both-Beam) | Beam-1 &<br>Beam-2<br>allowed to<br>circulate | Beam operation<br>NOT permitted <b>OR</b><br>dump request<br>for Beam-1 & Beam-2 | All required User Systems<br>for Beam-1 <b>OR</b><br>Beam-2 operation are<br>available | At least one required<br>Beam-1 AND<br>At least one required<br>Beam-2 User System is<br>unavailable |  |

Table 1: USER\_PERMIT and BEAM\_INFO Descriptions for LHC

**N.B** The safety requirements of the BIS dictate the internal architecture for the transmission of information from the User System to the LHC Beam Dumping System. This action meets at least *SIL 3* of the *IEC 61508* standard. However, it must be noted that the BEAM\_INFO signal provided by the CIBU has **no such safety requirement**.

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 8 of 22

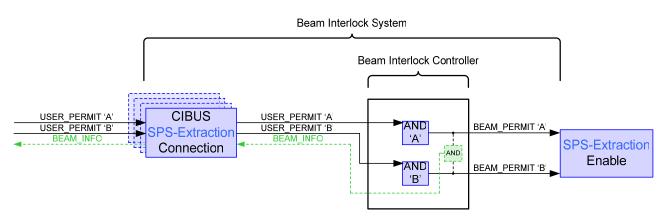

Figure 1: Simplified Internal Architecture of the LHC Beam Interlock System

The role of the CIBU is simply to transmit the USER\_PERMIT signals to the nearest Beam Interlock Controller in a safe and reliable manner, the redundant channels are labelled as 'A' and 'B' in the diagram. Connections to the LHC Injection System are not shown for simplicity.

The LHC BIS is made from 16 *Beam Interlock Controllers* (**BICs**) distributed around LHC. Each one performs the logical 'AND' of USER\_PERMIT signals from the connected User Systems. A very simplified version with only three connected systems is shown above, the BIC is able to connect with many more.

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 9 of 22

### 2.2 INTERLOCKING THE SPS RING

In the SPS, the Beam Interlock System generates a single BEAM\_PERMIT signal: When BEAM\_PERMIT is TRUE

» SPS Beam is allowed to circulate, and SPS injection is permitted.

When BEAM\_PERMIT is FALSE

» An SPS beam dump is requested (when BEAM\_PERMIT *changes* to FALSE) More information is given in the dedicated engineering specification [3].

The SPS CIBU transmits the USER\_PERMIT signals in a reliable and safe manner to the nearest Beam Interlock Controller to produce the SPS BEAM\_PERMIT signal. In return it provides Users with the BEAM\_INFO giving an indication of the availability of the SPS ring for beam operation:

| CIBU Type | USER                                | PERMIT                                                                   | BEAM_INFO                                                 |                                                                    |

|-----------|-------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|

| CIDO Type | TRUE                                | FALSE                                                                    | TRUE                                                      | FALSE                                                              |

| CIBUS     | SPS-Beam<br>allowed to<br>circulate | Beam operation<br>NOT permitted<br><b>OR</b><br>SPS-Beam<br>dump request | All required<br>SPS-Beam<br>User Systems are<br>available | At least one required<br>SPS-Beam<br>User System is<br>unavailable |

Table 2: USER\_PERMIT and BEAM\_INFO Descriptions for SPS

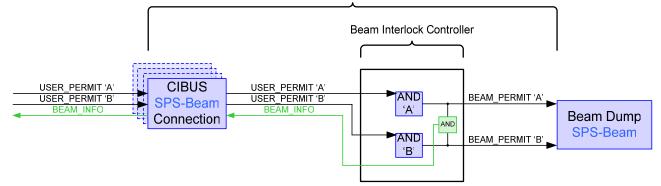

The SPS BIS has a simplified architecture, but the same safety level as the LHC BIS. A single connected system is shown in the drawing below

Beam Interlock System

Figure 2: Simplified Internal Architecture of the SPS Beam Interlock System

The SPS BIS is composed of 6 *Beam Interlock Controllers* (*BICs*) one installed in each BA building. Each controller performs the logical 'AND' of USER\_PERMIT signals from the locally connected User Systems.

This is exactly the same hardware as the other Beam Interlock Systems, simply without the Beam-2 modules, as SPS has only one Beam. As a result, the function of the SPS BIS is identical to the LHC BIS: when any USER\_PERMIT is removed, the Beam Dump is fired and the Beam is extracted.

Page 10 of 22

### 2.3 INTERLOCKING THE SPS EXTRACTION AND TRANSFER LINES

The role of the SPS Extraction Lines BIS is to enable beam extraction when all of the Extraction Line systems are ready. SPS Extraction is blocked if at least one system is not available. The same system is used for both SPS Extraction zones.

The BIS managing the SPS Extraction and Transfer Lines is based on a different architecture than the others:

- Several "slave" BICs, each interlocking a transfer line or part of one.

#### Connected to

- One "Master" BIC receiving the signal from the "slave" BICs and generating a BEAM\_PERMIT signal for the dedicated Extraction Kicker system:

When BEAM\_PERMIT is TRUE

» SPS Extraction is permitted.

When **BEAM\_PERMIT** is FALSE

» SPS Extraction is not permitted.

More information is given in the dedicated engineering specification [4].

The Role of the CIBU in this case is to safely and reliably transmit the USER\_PERMIT information to the nearest "slave" Beam Interlock Controller:

| CIBU Type | USER_PERMIT                  |                                  | BEAM_INFO      |                |

|-----------|------------------------------|----------------------------------|----------------|----------------|

| ство туре | TRUE                         | FALSE                            | TRUE           | FALSE          |

| CIBUS     | SPS-Extraction is<br>allowed | SPS-Extraction is<br>NOT allowed | See note below | See note below |

Table 3 : USER\_PERMIT and BEAM\_INFO Descriptions for SPS Extraction Lines

**Note:** The SPS Extraction Line BIS is based on hierarchy and its function is based on a windowed approach, with long periods of BEAM\_PERMIT = FALSE followed by millisecond bursts of BEAM\_PERMIT = TRUE when extraction is being made.

For these reasons BEAM\_INFO is maintained in the SPS Extraction and Transfer Lines solely for hardware compatibility reasons.

Figure 3: Simplified Architecture of SPS Extraction and Transfer Lines Interlock System

The BIS managing the SPS Extraction and Transfer Lines is using the same hardware as all other Beam Interlock Systems.

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 11 of 22

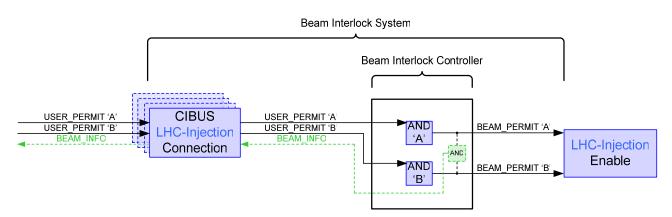

#### 2.4 INTERLOCKING THE LHC INJECTION

For the LHC Injection zones, the Beam Interlock System generates a single BEAM\_PERMIT signal:

When **BEAM\_PERMIT** is TRUE

» LHC injection is permitted.

When BEAM\_PERMIT is FALSE

» LHC Injection is blocked.

More information is given in the dedicated engineering specification [3].

The CIBU transmits the USER\_PERMIT signals in a reliable and safe manner to the nearest Beam Interlock Controller to produce the INJECTION BEAM\_PERMIT signal. In return it provides Users with the BEAM\_INFO giving an indication of the availability of the injection operation:

| CIBU Type | USER_PERMIT                 |                                 | BEAM_INFO      |                |

|-----------|-----------------------------|---------------------------------|----------------|----------------|

| ство туре | TRUE                        | FALSE                           | TRUE           | FALSE          |

| CIBUS     | LHC-Injection is<br>allowed | LHC-Injection is<br>NOT allowed | See note below | See note below |

| Table 4: USER | PERMIT | and BEAM | INFO | Description | s for LH | C Injection |

|---------------|--------|----------|------|-------------|----------|-------------|

|               |        |          |      |             |          |             |

The LHC Injection BIS has same safety level as the LHC BIS, the Injection BIS gives a windowed BEAM\_PERMIT, with long periods of BEAM\_PERMIT = FALSE followed by millisecond bursts of BEAM\_PERMIT = TRUE when injection is being made.

For these reasons BEAM\_INFO has little real meaning in the injection controllers. It is maintained only for compatibility.

Figure 4 : Simplified Internal Architecture of the LHC Injection Interlock system

The LHC Injection BIS is composed of only one *Beam Interlock Controller* (**BIC**) installed in each LHC injection region (SR2 and SR8). Each controller performs the logical 'AND' of USER\_PERMIT signals from the locally connected User Systems.

As a result, when any USER\_PERMIT is FALSE, the corresponding LHC Beam Injection is blocked.

Page 12 of 22

## **3. DESCRIPTION OF THE USER CONNECTION**

To maintain the safety requirements of the Beam Interlock System, the method of connection of User Systems is very particular. Effort has been made to create a simple, reliable and versatile input structure: taking into consideration the variety amongst equipments and the times of response required by the whole system.

#### 3.1 THE DIFFERENT TYPES OF USER SYSTEMS

There are many different types of hardware platform that will be connected directly to the BIS, equipment ranges from standard VME based approaches through Compact PCI, operating with TTL logic at around 5V, to PLC based systems where the common output voltage is 24V or a current loop. Overall the User Systems can be generalised into the following two categories:

| Main Hardware | <b>Operating Voltage</b><br>(Volts) | Speed Of Response<br>(relative) | Permit Change<br>Time |

|---------------|-------------------------------------|---------------------------------|-----------------------|

| PLC System    | 24                                  | Slow                            | ~1-10ms               |

| VME System    | 5                                   | Fast                            | ~0-5µs                |

Table 5: Basic Types of User System

The input circuit of the User Interface accommodates these systems with the same interface.

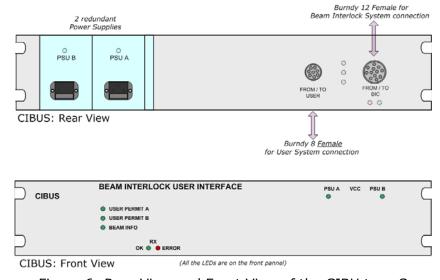

### 3.2 HARDWARE INTERFACE SUPPLIED TO THE USER SYSTEMS

The User Interface (*CIBU*) hardware is provided to all Users who need to connect to any Beam Interlock System. It consists of a *19" rack mounted* board, having a height of *2U*.

It will be mounted at the front of the Users Rack, with all electrical connections made <u>at the rear</u> of the CIBU panel, only status LEDs are visible from the front.

The CIBU variants completely serve all different types of User: LHC ring, LHC Injection, SPS ring and SPS Extraction Lines.

Therefore, the User Interface is available under 2 versions:

- CIBU**S**: **single** connection for interlocking a single Beam or Both-Beam.

- CIBU**D: double** connections for interlocking Beam-1 or Beam-2.

<u>Note:</u> The CIBUD and the CIBUS use exactly the same internal hardware. As the CIBUS has single connection, it has simply half of the components (the Beam-2 part is not assembled).

In both cases, the CIBU contains fully redundant power supplies and the hardware within the panel can be tested and monitored at distance.

### 3.2.1 THE CIBUD

The CIBU type  $\mathbf{D}$  (i.e. CIBUD) is only used in the LHC. It permits to connect LHC User System that is interlocking Beam-1 and Beam-2 independently.

The User connects to the BIS *twice*, once for each Beam. This connection is made in the **same CIBUD** but via a separate cable with a different gender connector and socket.

Figure 5: Rear View and Front View of the CIBU type D

### 3.2.2 THE CIBUS

The CIBU type  $\mathbf{S}$  (i.e. CIBUS) is used for SPS ring, for LHC Injection and for Extraction and Transfer Lines between SPS and LHC/CNGS. In all cases, there is only one beam.

The CIBUS is also used in the LHC for those Users that are interlocking Beam-1 and Beam-2 <u>simultaneously</u>. The User connects once, with a Both-Beam link. In case of USER\_PERMIT = FALSE, both beams would be extracted.

Figure 6: Rear View and Front View of the CIBU type S

The *socket* genders are noted on the two Figures on this page.

Page 14 of 22

Figure 7: CIBUD Rear View

When viewed from the rear, the Beam-2 sockets are on the left hand-side, Beam-1 on the right.

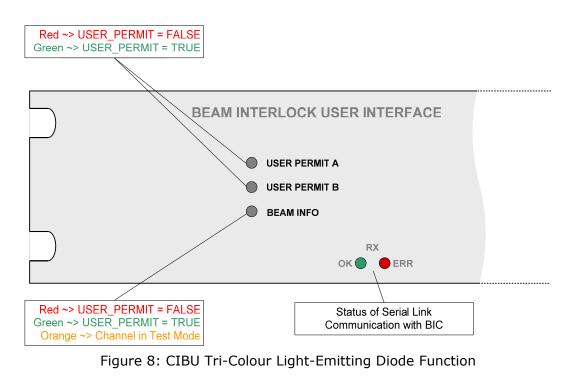

#### 3.2.3 THE CIBU LEDS

Various CIBU Light-Emitting Diodes are visible on the front panel. The important LEDs to note are those representing USER\_PERMIT 'A', USER\_PERMIT 'B' and BEAM\_INFO. These are Tri-Colour LEDs having the functions shown in the following diagram:

Page 15 of 22

## 4. ELECTRONIC INTERFACE REQUIRED WITH THE USER SYSTEMS

### 4.1 GIVING USER\_PERMIT

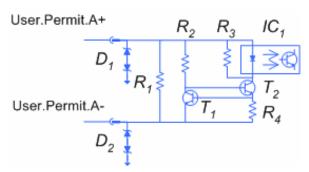

As the safety and reliability requirements of the BIS are strict, there are many rules to follow concerning the interface to the User System. The redundant USER\_PERMIT signals **'A'** and **'B'** are generated by two separate current loops from the User System, for each of the two current loops the following applies:

| Input Loop Current <sup>iii</sup><br>(mA) | USER_PERMIT<br>(Boolean)                              |

|-------------------------------------------|-------------------------------------------------------|

| < 1                                       | FALSE (user <b>DOES NOT</b> give permission for beam) |

| ≥ 9                                       | TRUE (user gives permission for beam)                 |

Table 6: Function of the Input Current Loops for USER\_PERMIT

Note that between the values of 1 and 9 milliamps, the value of USER\_PERMIT is either TRUE or FALSE, depending on the age of the installed equipment. A newer optocoupler will react to lower levels of current, whereas an ageing device will have a higher threshold of current.

#### Essentially USER\_PERMIT is guaranteed FALSE when the current is less than one milliamp, it is guaranteed TRUE when the current is greater than nine milliamps.

Figure 9: Current Loop for USER\_PERMIT

| Component<br>Name | Value    | Туре            |  |

|-------------------|----------|-----------------|--|

| $D_1$             | 33V (Bi) | TVS +/-33V (BD) |  |

| D <sub>2</sub>    | 33V (Bi) | TVS +/-33V (BD) |  |

| $R_1$             | 18kΩ     | 125mW           |  |

| R <sub>2</sub>    | 20kΩ     | 125mW           |  |

| R <sub>3</sub>    | 1k2Ω     | 125mW           |  |

| R <sub>4</sub>    | 56Ω      | 125mW           |  |

| $T_1$             | -        | BC847           |  |

| T <sub>2</sub>    | -        | PZT2222         |  |

| IC <sub>1</sub>   | _        | HCPL-2601       |  |

Table 7 : Component List for USER\_PERMIT

The User System needs to provide sufficient voltage across USER.PERMIT.A+ and USER.PERMIT.A-. Around 12mA will be drawn through the optocoupler, this is regulated by the transistor  $T_1$  in conjunction with  $R_4$ , which turns off  $T_2$  when the voltage drop across  $R_4$  is too high.  $R_3$  forces the optocoupler off in low current situations, as the optocoupler requires around 1.2V across its diode before switching.

$R_1$  ensures that floating inputs cannot cause USER\_PERMIT to change value. Note also that a pair of Transient Voltage Suppressors ( $D_1$  and  $D_2$ ) is used to protect the input of the circuit. These activate when the line voltage is outside of the range +/-33V. Circuit USER\_PERMIT 'B' is identical.

<sup>&</sup>lt;sup>iii</sup> No tolerance is given for the current level, it is resulated by a transistor pair

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 16 of 22

## 4.2 READING BEAM\_INFO

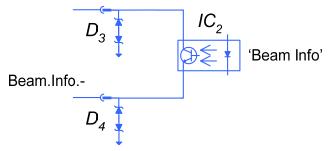

The  ${\tt BEAM\_INFO}$  is returned to the User in the form of an optocoupler which is driven by the CIBU:

| Transistor Status | BEAM_INFO<br>(Boolean)                   |  |

|-------------------|------------------------------------------|--|

| Open              | TRUE (beam is allowed to circulate)      |  |

| Closed            | FALSE (beam is NOT allowed to circulate) |  |

Table 8: Function of the Output Transistor for BEAM\_INFO

Beam.Info.+

| Component<br>Name | Value Type |                 |

|-------------------|------------|-----------------|

| D <sub>3</sub>    | 33V (Bi)   | TVS +/-33V (BD) |

| D <sub>4</sub>    | 33V (Bi)   | TVS +/-33V (BD) |

| IC <sub>2</sub>   | -          | SFH 618A-5      |

Table 9: Component List for BEAM\_INFO

Figure 10: Optocoupler for BEAM\_INFO

When the CIBU allows current to flow in the optocoupler, the transistor is activated, giving an indication to the user of the status of the Beam Permit within the BIS.

The failure modes of this circuit mean that <u>this signal cannot be used for</u> <u>safety critical operations</u>. If a User wants to be sure that no beam circulates in the LHC, the USER\_PERMIT must be set to FALSE.

This circuit is also protected by Transient Voltage Suppressor Diodes that activate when the signal exceeds +/-33V.

### 4.3 PINOLOGY OF CIBU SOCKETS

The socket on the *User Interface* (*CIBU*) for the connection from/to the *User System* is a **Burndy 8-Pin UT07**. The pinology of the socket is shown in the table directly below, with the schematic on the right:

| PIN    | Schematic<br>Name | Function                                  |  |

|--------|-------------------|-------------------------------------------|--|

| 1      | GND               | EMC improvement<br>by ground<br>proximity |  |

| 2      | GND               | EMC improvement<br>by ground<br>proximity |  |

| 3      | User.Permit.A+    | Current Loop + for<br>USER_PERMIT 'A'     |  |

| 4      | User.Permit.A-    | Current Loop – for<br>USER_PERMIT 'A'     |  |

| 5      | User.Permit.B+    | Current Loop + for<br>USER_PERMIT 'B'     |  |

| 6      | User.Permit.B-    | Current Loop – for<br>USER_PERMIT 'B'     |  |

| 7      | Beam.Info.+       | BEAM_INFO +<br>collector                  |  |

| 8      | Beam.Info         | BEAM_INFO -<br>emitter                    |  |

| Shield | GND               | EMC improvement<br>by enclosure           |  |

Table 10: Pinology of CIBU User Connection

Schematic

For the CIBUS, the above socket is always a Burndy 8-Pin **female**.

For the CIBUD, it's either a Burndy 8-Pin **female** (Beam-1) or Burndy 8-Pin **male** (Beam-2). This is intentional so that User Systems capable of dumping the LHC beams individually cannot misconnect the Beam-1 and Beam-2 signals.

Page 18 of 22

### 4.4 USER SYTEM TO BIS INPUT/OUTPUT SPECIFICATIONS

The circuit on the previous page shows the complete interface, care must be taken not to exceed the specification of any of the components used, in particular the optocouplers for the user permit signals.

#### 4.4.1 GUARANTEED INPUT SPECIFICATIONS

| Name                       | Description                                                        | Value               |

|----------------------------|--------------------------------------------------------------------|---------------------|

| V <sub>ins</sub> (max)     | Maximum voltage allowed on a single USER.PERMIT.+ or line          | 33 V                |

| V <sub>in</sub> (max)      | Maximum Voltage allowed from USER.PERMIT.+ to USER.PERMIT          | ~25V                |

| V <sub>in</sub> (min)      | Minimum voltage needed across circuit for USER_PERMIT = TRUE       | ~3 V                |

| V <sub>in</sub> (rev)      | Maximum negative Voltage allowed from USER.PERMIT.+ to USER.PERMIT | 5V                  |

| dV <sub>in</sub> /dt (max) | Maximum rate of change of V <sub>in</sub> with respect to time     | 5000 V/µs           |

| I <sub>intrue</sub> (min)  | Minimum current from USER.PERMIT.+ to for USER_PERMIT = TRUE       | 9 mA                |

| I <sub>intrue</sub> (max)  | Maximum current from USER.PERMIT.+ to for USER_PERMIT = TRUE       | ~15mA               |

| $I_{infalse}$ (max)        | Maximum current from USER.PERMIT.+ to for USER_PERMIT = FALSE      | 1mA                 |

| I <sub>in</sub> (reverse)  | Maximum negative current from USER.PERMIT.+ to                     | 10 µA <sup>iv</sup> |

| Δt (min)                   | Minimum signal length to change USER_PERMIT from TRUE to FALSE     | 2 µs                |

| SAFETY                     | Combined Safety of USER_PERMIT 'A' and 'B'                         | SIL 3               |

Table 11: CIBU Input Specifications

The current in the input stage is internally regulated by the CIBU; the guaranteed values of current are shown in the table above. Note that a digital filter is applied to the USER\_PERMIT signal, removing  $2\mu$ s of state change from TRUE to FALSE.

#### A Note for PLC Users:

**1.** The dV/dt maximum means the use of mechanical relays for driving the input circuits should be avoided.

2. Applying a reverse voltage of 24V to the input circuit (for example swapping pins 3 and 4 by accident) will damage the CIBU.

#### 4.4.2 GUARANTEED OUTPUT SPECIFICATIONS

| Name                           | Description                                             | Value   |

|--------------------------------|---------------------------------------------------------|---------|

| V <sub>out</sub> (max)         | Maximum voltage from BEAM.INFO.+ to                     | 27 V    |

| V <sub>out</sub> (max reverse) | Maximum negative voltage from BEAM.INFO.+ to            | 6 V     |

| I <sub>out</sub> (max)         | Maximum current BEAM.INFO.+ to                          | 50 mA   |

| $\Delta t_{on}$ (max)          | Maximum time for BEAM_INFO to change to TRUE from FALSE | 140 µs  |

| $\Delta t_{off}$ (max)         | Maximum time for BEAM_INFO to change to FALSE from TRUE | 120 µs  |

| SAFETY                         | Combined Safety of BEAM_INFO                            | < SIL 1 |

Table 12: CIBU Output Specifications

Note that **BEAM\_INFO does not meet ANY of the Safety Integrity Levels of the IEC-61508**, it should be used for information only and in no case must BEAM\_INFO be solely used to influence either USER\_PERMIT signal.

$^{\rm iv}$  Through optocoupler, I = V/18000 will also flow through R1

#### AB-CO-Note 06-XX 1v4 (Tech.)

Page 19 of 22

## **5. USER REQUIREMENTS**

#### 5.1 POWERING THE CIBU

The User must provide **two 230V mains supply sockets** within a distance of approximately **1.5m** of the rear of the CIBU, for the redundant Power Supply Units.

#### 5.2 USER SYSTEM TEST ON DEMAND

For the commissioning, installation and cold check-out of the CIBU, the User System must also be able to change the state of USER\_PERMIT 'A' and USER\_PERMIT 'B' from TRUE to FALSE on demand. This will verify the complete link from User System to BIS.

The reverse transition should not be possible<sup>v</sup> via any form of test mode; i.e. **Users should not be able to** *force* **both USER\_PERMIT = TRUE** if their system is not ready for beam operation.

In order to facilitate testing of the entire interlock chain, Users are permitted to set  $USER\_PERMIT A' = TRUE$ , but only when  $USER\_PERMIT B'$  is guaranteed to be FALSE.

Note that upon entering a Test Mode, User Systems should toggle USER\_PERMIT `A' and USER\_PERMIT `B' to FALSE to guarantee that the machine is without beam.

#### 5.3 USER SYSTEM SPECIFICATIONS OF INTERCONNECTION

The interconnection also dictates some of User System parameters:

Firstly, the User System must be capable of sourcing  $\sim 80mA$  to drive the input stages of the USER\_PERMIT signals and the BEAM\_INFO, Users should take care to restrict the current that can flow through the USER\_PERMIT lines, as a connector fault could drive one of these signals to ground during installation.

Secondly, the User should take care to add *Transient Voltage Suppressors* in the signal lines as transient voltage spikes could destroy unprotected User circuits.

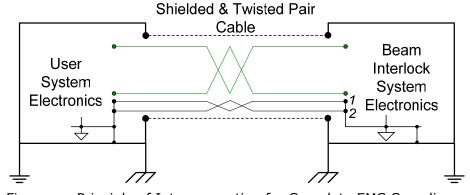

#### 5.4 EMC COMPLIANCE OF INTERCONNECTION

In order to avoid EMC problems, the connection from CIBU to User System must be correctly implemented. The connection is to be realised as follows:

Figure 12: Principle of Interconnection for Complete EMC Compliance

<sup>v</sup> This constraint is NOT applicable for User Systems that are interlocking the Extraction lines

Page 20 of 22

#### 5.4.1 THE INTERCONNECTING CABLE

The interconnecting cable needs to be a **shielded-twisted-pair** (NE 8 is a good example) passing in a sensible route from User System to Beam Interlock System. The cable should be stowed in cable-racks if the distance to travel exceeds around 1m. As a rule of thumb it should be no longer than **4m** as the CIBU should be as close as practically possible to the User System. Care should be taken **not to allow the cable to run in parallel to power cables**, as they will interfere. It should also be noted that the cable should **not run in parallel to conductors carrying very low voltage signals**, as the cable can be a source of interference, as well as a receptor.

#### 5.4.2 THE CONNECTORS

Conductive **metal connectors** are needed, which should mate with an electrically conductive chassis **without anodisation**. Whereevr possible a treatment such as alodine should be applied to make the metalwork more conductive. Note that standard front panels are NOT conductive. The shield of the cable should be connected **360°** around the connector, surrounding all the signal wires completely; **pig-tail connections for the shield are expressly forbidden**.

#### 5.4.3 THE EARTHING

The shield of the cable should be electrically connected to the chassis, which itself should form a protective box around the user equipment. The chassis should be connected to Earth with the shortest stubs possible, and in many places. The electronic ground of the User System should also be joined to Earth in many places, with short stubs. Internal connections are provided that link the ground of the Beam Interlock System with the User System. The electrical grounds of the Beam Interlock System and the User System should be connected together in all circumstances.

LHC Project Document No. AB-CO-Note 06-XX 1v4 (Tech.)

Page 21 of 22